<관련 포스팅>

HBM 메모리 개요 및 필요성, 기존 DRAM 메모리와의 차이점 - AI 반도체의 핵심

차세대 인터커넥션 기술과 관련주 - TSV본딩, 하이브리드 본딩과 와이어본딩, 플립칩본딩 비교

HBM 제조 공정 기술 분석 : ② MR-MUF와 TC-NCF 본딩 공정 특징, 차이점, 관련주

1. HBM 제조 공정

HBM은 완성된 DRAM Die (메모리 칩)을 수직으로 여러개 적층하고, TSV기술을 통해 칩 전면에 1024개의 미세한 전기 통로를 만들어 메모리 칩간의 고속, 대역폭의 신호 전달이 가능하게 한 반도체 칩 입니다.

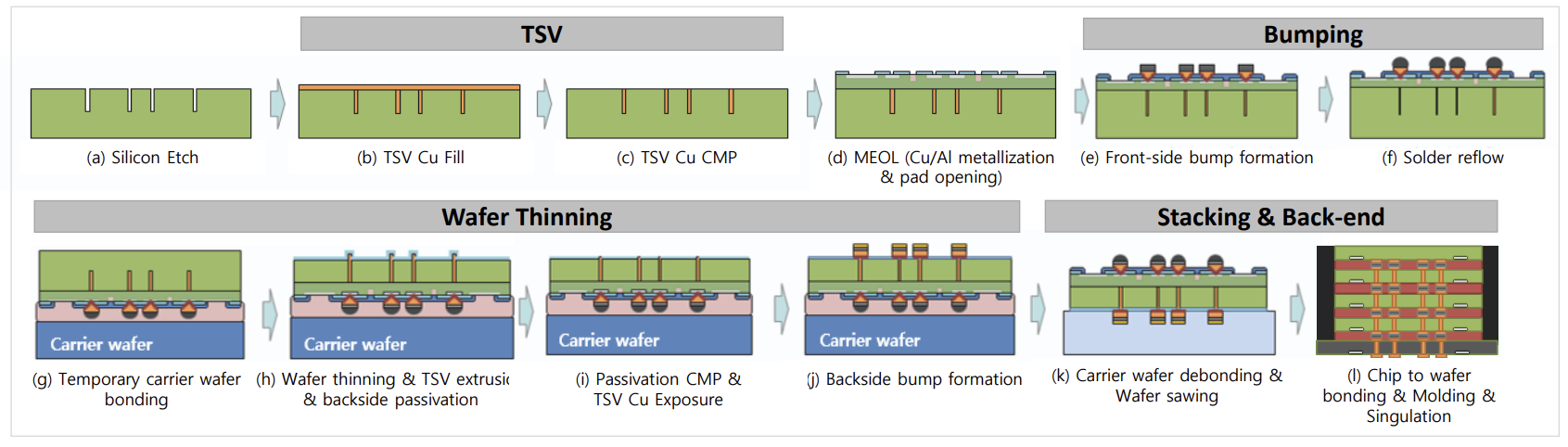

HBM의 제조 공정은 크게 ▲CMOS 셀 제조단계 (FEOL), ▲TSV 공정 단계, ▲금속 배선 공정 단계 (MEOL, BEOL), ▲Front-Side 범핑 공정, ▲웨이퍼 그라인딩(Grinding, Thining) 공정, ▲Back-Side 범핑 공정, ▲칩을 자르고(Dicing) 적층(Stacking)하는 공정으로 이루어집니다.

TSV 공정이 전공정 단계에서 이뤄지기 때문에 TSV 본딩 기술을 웨이퍼 레벨 패키징이라고도 합니다.

- FEOL(Front-End Of Line) : 메모리 반도체 역할을 하는 CMOS 셀 제조 단계

- TSV(Through Silicon Via) : 완성된 셀 구조에 수직으로 구멍을 뚫고 전기가 통할 수 있도록 구리를 채워주는 단계

- MEOL(Middle-End Of Line) & BEOL(Back-End Of Line) : 금속 배선 및 절연막 생성 단계, 마이크로범프 형성을 위한 알루미늄 패드를 만들어 줌

- Front-Side Bumping : 금속 배선 이후 다른 칩과의 접착 및 입출력 (I/O) 단자 형성을 위한 마이크로 범프 형성 단계

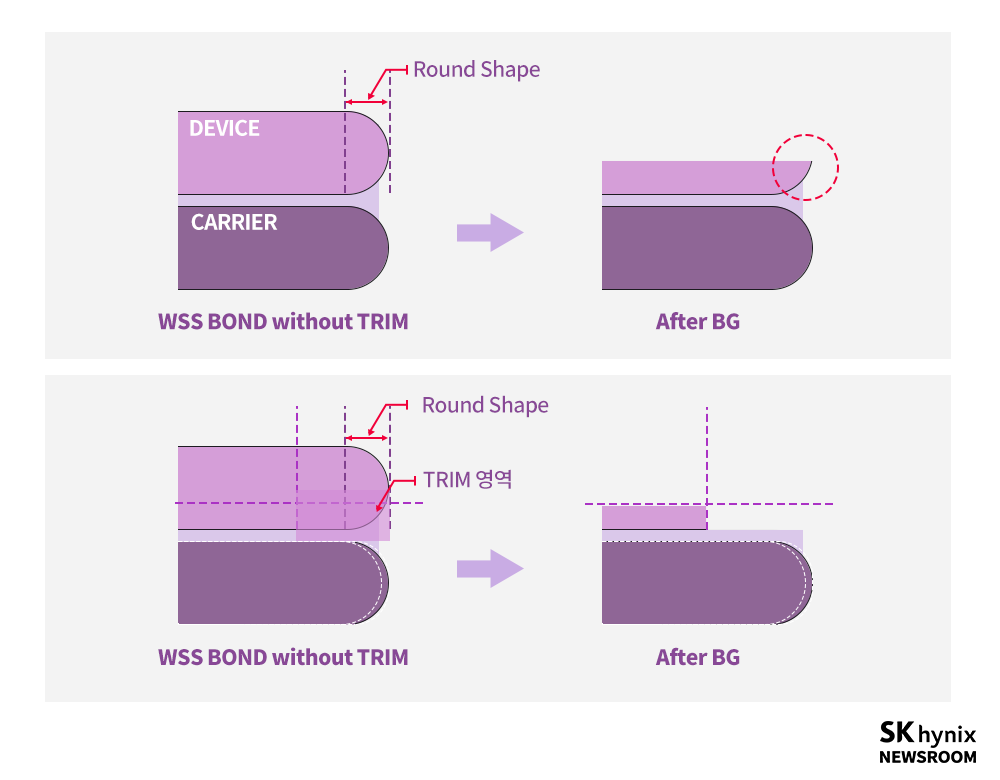

- WET (Wafer Edge Trimming) : 이후 공정에서 웨이퍼 후면을 그라인딩을 하고 나면 웨이퍼의 엣지 부분이 날카로워지고, 이는 공정 중에 깨질 수 있기 때문에 미리 가장자리를 깎아주는 공정

- WSS (Wafer Suporting System) : 이후 공정인 웨이퍼 그라인딩 시 웨이퍼가 휘거나 깨지는 것을 방지하고, 후면 범핑 공정을 진행하기 위해 캐리어 웨이퍼를 부착 및 탈착, 세정하는 공정

- Wafer Grinding (Thining) : 칩 후면 웨이퍼를 갈아서 TSV 통로가 노출되게 하는 단계

- Back-Side Bumping : 노출된 후면 TSV에 마이크로 범프를 형성하는 단계

- Dicing & Stacking : 웨이퍼에서 완성된 칩들을 잘라낸 후 서로 접합하여 수직으로 적층하는 단계

이번 포스팅에서는 TSV 공정과 마이크로 범핑 공정에 대해 알아보겠습니다.

2. TSV 공정 특징과 필요 기술

■ TSV의 특징과 장점

TSV(Through Silicon Via)는 웨이퍼(전공정) 단계에서 에칭공정을 통해 웨이퍼를 수직으로 뚫어 통로를 만든 후, 전도성 재료를 채워 도선이 위아래의 다른 칩과 연결될 수 있도록 하는 기술입니다.

칩을 적층할 때는 TSV 위아래에 솔더 범프(납땜)를 형성해 칩간 접합을 진행합니다.

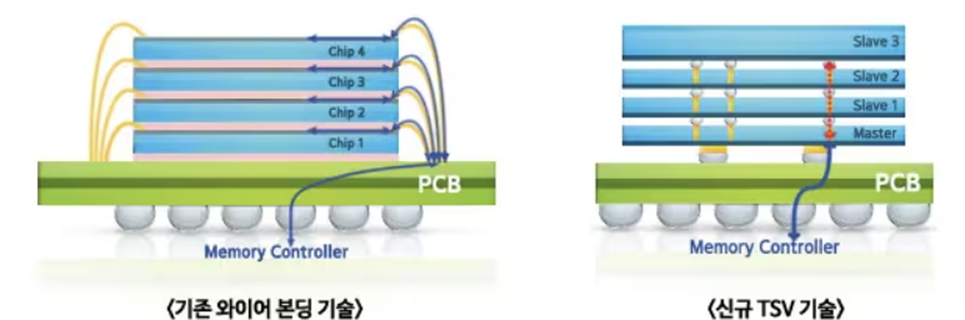

이런 TSV 본딩 기술을 통해 기존 인터커넥션 기술 (와이어 본딩, 플립칩 본딩) 대비 칩간 최단거리 형성을 통한 ▲속도 향상, ▲전력소비 감소, ▲발열 감소, ▲높은 I/O 밀도 형성을 통한 대역폭 확대가 가능해졌습니다.

기존 와이어 본딩 및 플립칩 본딩은 다른 칩과의 통신을 위해 반드시 기판(subtrate)를 통하기 때문에 신호 전달 경로가 길고 복잡했으며, 와이어가 지나갈 공간이 필요했습니다.

반면에 TSV는 칩과 칩이 곧바로 통신할 수 있는 엘리베이터와 같은 역할을 하게 됩니다.

TSV를 통해

공간 효율 ↑

입출력 I/O 개수 ↑

신호 전달 속도 ↑

■ TSV 공정 기술 난이도

그러나 이 TSV 기술을 통한 칩 적층은 수율관리가 매우 어렵습니다.

특히 칩을 스태킹하는 공정에서는 하나의 칩만 잘못돼도 모든 칩을 사용하지 못할 수 있습니다.

현재 TSV 공정을 마친 Wafer 수율은 50% 수준이라고 하며, 이를 적층해나갈수록 수율이 떨어지게 됩니다.

따라서 다음과 같은 부분에 높은 난이도의 기술 확보가 필요합니다.

- 높은 표면 청결도, 평탄도 필요

칩당 표면에 1024개씩 있는 미세한 I/O 홀(via)들을 칩끼리 정밀하게 접합하기 위해서는 높은 표면 청결도와 평탄도가 요구됩니다.

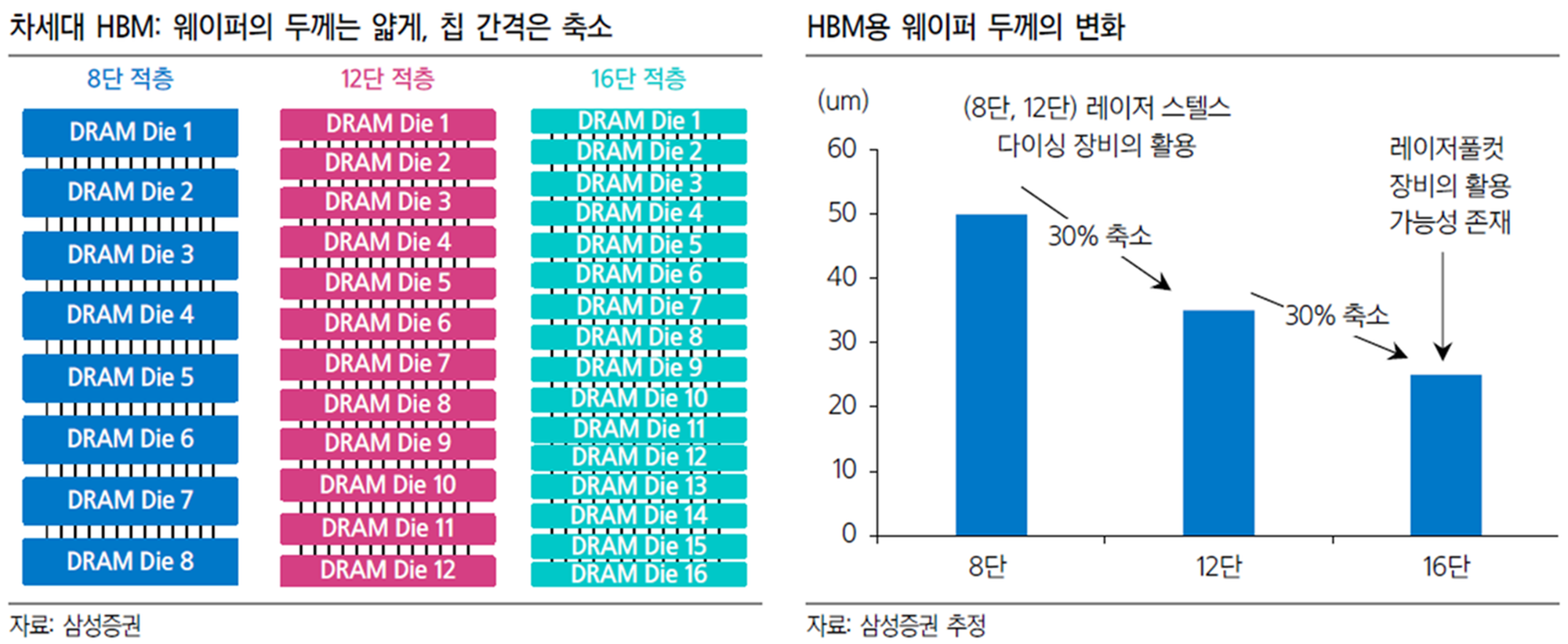

그러나 HBM의 적층 수를 높이기 위해서는 웨이퍼를 더 얇게 깎아야 하는데 (그라인딩), 웨이퍼 두께가 얇아질수록 와피지(휨)가 발생하거나 깨지는 현상이 발생합니다.

또한 웨이퍼를 깎으면서 생기는 불순물들로 오염이 될 수도 있습니다.

- 방열 관리

적층된 칩들의 밀도가 높아지면서 각 칩에서 생기는 열들이 칩 사이에 집중되는 문제가 생깁니다.

이를 위해 칩 중간중간 방열 경로를 설계하는 것에 높은 난이도를 요구하며, 소재 또한 내열성이 높은 소재 채택이 필요해집니다.

또한 TSV 이후, 칩끼리 접합하는 공정에서 고온의 열을 사용하는데, 이때도 열팽창계수 차이에 따른 웨이퍼 및 패키지 기판의 와피지(휨) 현상이 발생할 수 있습니다. - Via 균일도 및 Void 관리

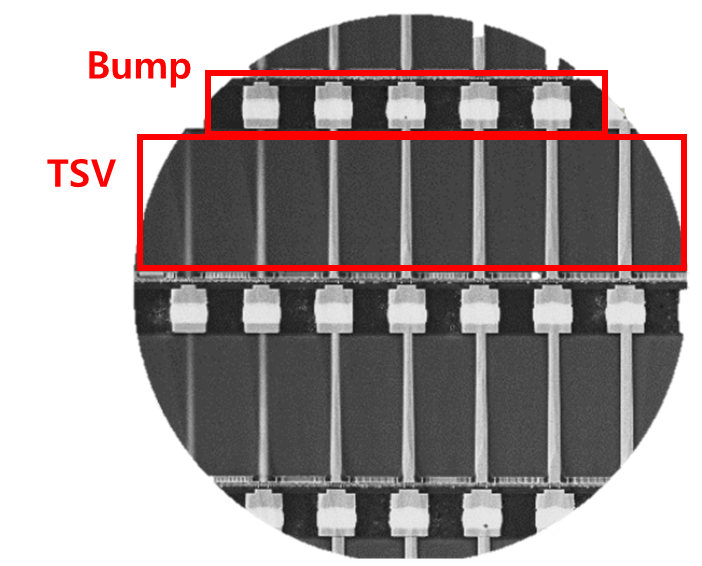

TSV는 에칭공정을 통해 칩 전면에 1024개의 미세한 구멍을 뚫는데, 이때 수직으로 균일하게 만들어져야합니다.

이후 구멍에 전기 이동을 위한 구리를 채워넣는데, 이때 중간에 빈 공간(void)가 생기지 않도록 균일하게 채워넣어야 이후 단선이나 단락 등의 불량이 발생하지 않습니다.

Via 직경이 더 미세화 될수록, Via의 균일도가 일정하지 않을수록 void 관리가 어려워집니다. - 진동 및 충격 보호

TSV 공정 이후 본딩을 통해 수직으로 칩 적층을 함에 따라 작은 진동 및 충격에도 TSV 연결에 손상이 갈 수 있습니다.

이는 곧 내구성과 신뢰성에 직결되기 때문에 이를 방지하는 기술 및 테스트 기술이 필요합니다.

웨이퍼의 구멍을 뚫는 TSV 공정은 주로 건식 식각 (Dry Etching) 기술을 쓰며, 이는 꽤 성숙화 단계의 기술입니다.

또한 HBM의 칩 적층 수가 높아지면서 웨이퍼를 더 많이 깎아야하기 때문에, 상대적으로 TSV의 깊이는 완화되고 있는 추세 입니다.

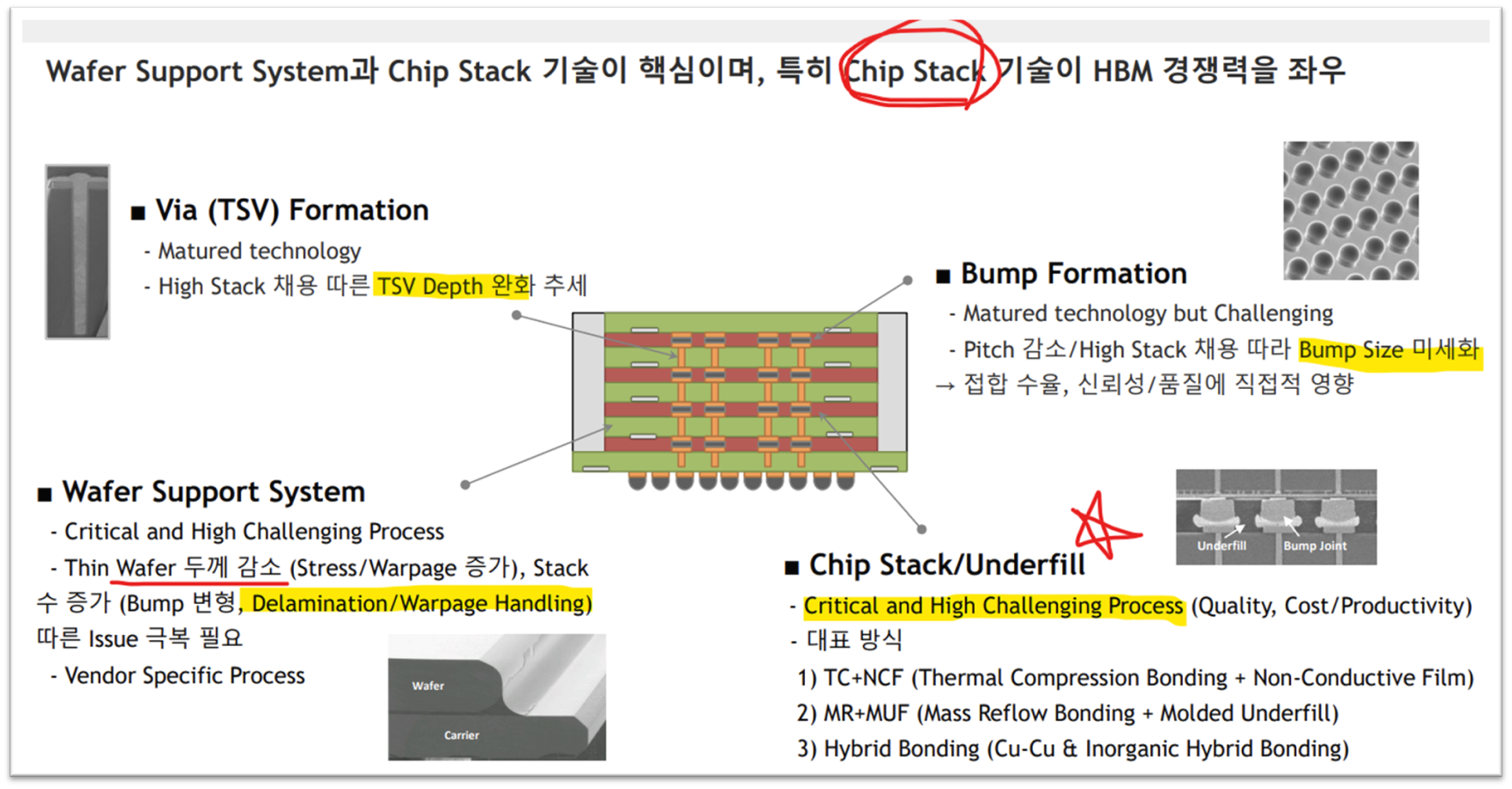

따라서 TSV 공정 자체는 깊이보다는 미세화와 via 간 pitch 감소, TSV 개수 증가에 따른 솔더 범프 크기 감소가 주된 이슈입니다.

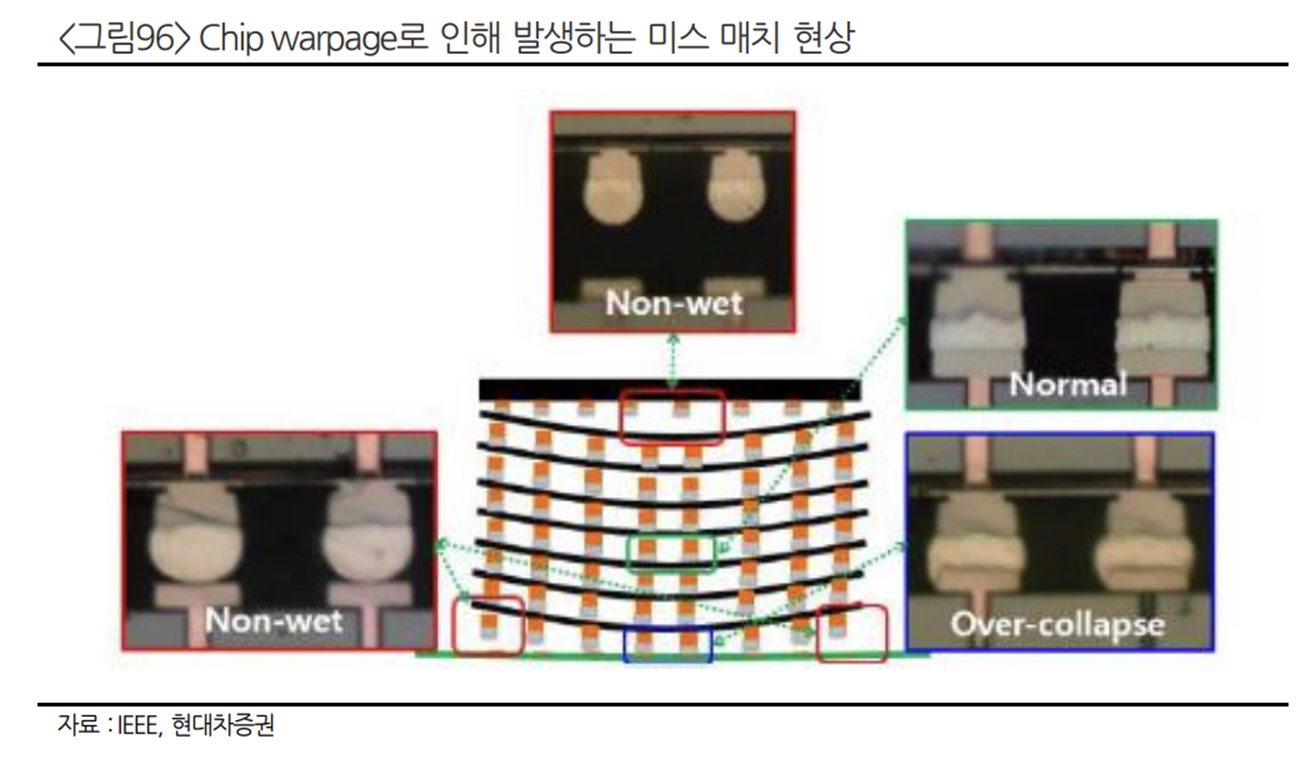

다만 TSV 이후 웨이퍼의 휨(Warpage)과 깨짐을 방지하고, 적층 시 칩과 칩 간의 본딩 정렬 정밀화, 방열 이슈 개선하는 기술이 가장 챌린징한 상황이며 HBM의 수율과 성능, 신뢰성에 가장 핵심이 되는 기술입니다.

3. 마이크로 범프

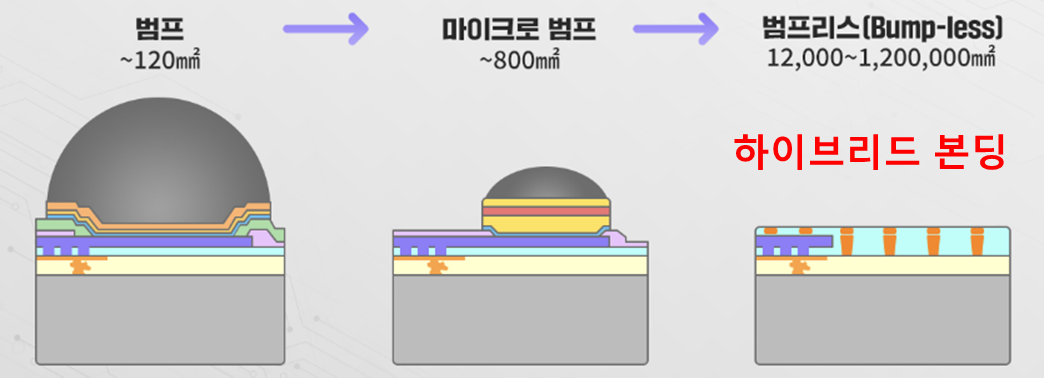

HBM의 칩 간 TSV가 연결되는 부분은 20um(마이크로미터) 크기의 솔더 범프(Solder Bump)로 연결되며, 이는 곧 칩간의 본딩 접착제이자 신호의 입출력 단자 (I/O 핀)가 됩니다.

마이크로 범프가 중요한 이유는, 단위 면적당 입출력 단자 개수를 늘리려면 칩간 연결 부분인 범프의 크기가 작아져야하기 때문입니다.

즉, 단위 면적당 범프 집적도를 높이는 것이 대역폭을 증가시키는데 가장 핵심이 됩니다.

최근 마이크로 범프에 사용되는 기술은 CPB(Copper Pillar Bump)로, 구리 기둥을 만들어서 칩과 칩, 칩과 기판 사이의 간격(Bonding Gap)을 높이고, 대신 범프(Bump)의 크기를 줄여 범프 간 간격을 줄이는 기술입니다.

이를 통해 범프끼리 붙어서 단락이 발생하는 것을 방지할 수 있습니다.

HBM에서 마이크로 범프 공정의 문제는 언더필(Under Fill) 공정과 본딩(Bonding) 공정입니다.

언더필 공정은 본딩 이후 범프 피치간 공간을 폴리머 등으로 채워 접합부의 신뢰성과 안정성을 높이고, 칩간, 칩과 기판 간 열팽창 계수 차이에 따른 스트레스 완화, 절연 및 방열 특성 강화를 위해 수행 하는 공정입니다.

그러나 향후 HBM의 TSV 개수가 많아지면서 범프 간 피치가 지금보다 더 줄어들게 되면 언더필 공정 중에 범프끼리 붙게되거나 언더필 재료가 칩 중간 부분의 피치 공간까지 균일하게 채우지 못하는 등의 문제가 발생하게 됩니다.

열압착(TC : Thermo Compression) 및 리플로우(MR : Mass Reflow) 방식 등을 사용하는 본딩 공정에서도 본딩 과정에서의 고온 및 압력 전달에 따른 칩 손상, TSV 정렬 틀어짐 등의 이슈가 발생할 수 있습니다.

이러한 문제로 차세대 HBM에는 범프를 형성하지 않고 (Bumpless), 칩과 칩, 칩과 기판 사이의 구리를 직접 접합하는 하이브리드 본딩 기술이 차세대 인터커넥션 방식으로 각광받고 있습니다.

'산업 및 기업 분석 > 반도체·디스플레이' 카테고리의 다른 글

| [HBM 파헤치기기] HBM 제조 공정 기술 분석 : ③ 핵심은 발열과 웨이퍼 와피지 컨트롤 (1) | 2024.06.07 |

|---|---|

| [HBM 파헤치기] HBM 제조 공정 기술 분석 : ② MR-MUF와 TC-NCF 본딩 공정 특징, 차이점, 관련주 (4) | 2024.05.19 |

| [어드밴스드 패키징] 차세대 인터커넥션 기술과 관련주 - TSV 본딩, 하이브리드 본딩과 와이어 본딩, 플립칩 본딩 비교 (0) | 2024.05.15 |

| [HBM 파헤치기] HBM 메모리 개요 및 필요성, 기존 DRAM 메모리와의 차이점 - AI 반도체의 핵심! (2) | 2024.03.10 |

댓글