<관련 포스팅>

HBM 제조 공정 기술 분석 : ① TSV(실리콘관통전극) 본딩과 마이크로범프 (차세대 인터커넥션 기술)

HBM 제조 공정 기술 분석 : ② MR-MUF와 TC-NCF 본딩 공정 특징, 차이점, 관련주

HBM 메모리 개요 및 필요성, 기존 DRAM 메모리와의 차이점

차세대 인터커넥션 기술과 관련주 - TSV본딩, 하이브리드 본딩과 와이어 본딩, 플립칩 본딩 비교

1. AI, 발열을 잡는 것이 중요

데이터센터는 높은 안전성과 데이터 신뢰성이 요구되며, 운영 비용의 90% 비중을 차지하는 막대한 전력 비용을 감축하는 것이 중요합니다.

특히 AI로 인해 데이터센터 내 GPU 사용량이 많아지고, 그에 따른 전력밀도가 높아지면서 자연스럽게 열 방출량이 높아지게 됩니다.

현재 데이터센터 전력 사용량 중 약 40%가 발열을 잡기 위한 냉각 시스템에 사용되고 있습니다.

따라서 발열을 냉각시키기 위한 에너지를 줄이는 기술들이 가장 핵심적인 요소로 떠오르고 있습니다.

이에 현재 구글, 마이크로소프트, 아마존 등 빅테크 기업들의 데이터센터에 들어가는 고성능 컴퓨팅 서버 (HPC)의 가장 핵심적인 요구사항은 반도체 칩의 발열을 잡는 기술입니다.

발열은 반도체 칩의 성능과 신뢰성에 가장 큰 적이며, 발열이 높아질수록 전력소모량도 커지기 때문입니다.

그러나 현재의 반도체 칩들은 공정미세화가 진행되고, 요구 속도 또한 크게 증가하면서 단위 칩 면적당 전력 밀집도가 매우 크게 증가했고, 그에 따른 발열을 잡는 것이 점차 어려워지고 있습니다.

칩의 온도가 올라가게 되면 타이밍 오류나 메모리 수명에 영향을 주며, 누설 전류가 생기면서 데이터 오류가 발생할 확률이 높아져 제품의 신뢰성이 하락하고 전력 소모량이 더 커지게 됩니다.

특히 휘발성인 DRAM 메모리의 경우 셀 내에 데이터를 유지하기 위해 주기적으로 전류를 충전해주어야 하는데,

이때 발열이 커지면 누설전류가 증가하게 되고, 이에 따라 더 자주 데이터 유지를 위한 셀 리프레쉬가 이루어져야하므로 전력소모가 증가하는 악순환이 발생합니다.

또한 리프레쉬 동작을 하는 중에 해당 셀 사용이 제한되므로 칩의 사용 가능한 용량과 속도가 떨어지게 됩니다.

발열 증가시

- 데이터 손실 ↑

- 셀 접근 시간 ↑ (속도 ↓)

- 반도체 소자 열화에 따른 수명 ↓

- 과부하에 따른 시스템 오류 ↑

- 전력 소모량 ↑

더군다나 HBM은 이런 DRAM 메모리 칩을 수직으로 적층하면서, 각 메모리 칩에서 발생한 열이 칩 간 층 사이에 갇혀 빠져나오기 힘든 구조입니다.

또한 HBM의 세대가 진화하면서 단일 HBM에 적층되는 메모리 칩 개수는 8개에서 16개로 증가하게 되고, 그에 따라 칩간 간격이 좁아지면서 열 에너지 밀집도가 높아지므로, 발열 컨트롤하는 것이 더욱 중요해지게 됩니다.

2. HBM 발열 컨트롤

■ TSV 공정

HBM은 칩 전면에 TSV라는 수천개의 입출력 통로를 수직으로 뚫어 메모리 칩간 데이터가 전송될 수 있게 합니다.

이때 TSV는 데이터 전송 통로일 뿐만 아니라 각 칩에서 발생된 열을 아래쪽으로 전달해 방출될 수 있도록 도움을 줍니다.

■ 더미 범프 (열 범프)

HBM의 각 칩 사이에는 칩 간 TSV 통로를 연결하고 접합하기 위한 솔더 범프 (납땜)가 존재합니다.

이러한 TSV 연결 범프 외에 열 배출을 용이하게 하고 구조적인 안정성을 제공하기 위한 더미 범프(Dummy Bump, Thermal Bump)를 칩 사이사이에 설치해 열 전달 경로를 늘리고, 적절하게 분산되어 한 곳에 열이 집중되지 않도록 해줍니다.

■ 방열용 언더필 소재

절연 및 물리적 안정화를 위해 HBM Die 칩 사이사이를 매꿔주던 언더필 (Under Fill) 소재는 주로 에폭시나 폴리머 소재로, 방열 특성을 높이기 위한 여러 재료들이 사용되고 있습니다.

방열용 언더필 재료로는 대표적으로 실리카, 알루미나, BeO, AlN, SiC, BN 등이 있습니다.

현재 삼성전자와 SK하이닉스의 HBM에 사용되는 언더필 형태는 필름 형태인 삼성전자의 NCF와 액체 형태인 SK하이닉스의 MUF로 나뉘고 있습니다.

SK하이닉스의 MUF에 사용되는 소재가 삼성전자의 NCF 소재 대비 방열 특성이 높다고 하는데, 이는 MUF(Molded Under Fill) 공정 특성상 액체 형태의 액상 몰딩 기법 (LCM, Liquid Compression Molding)이 사용되고, Film 형태의 NCF 보다 열 존도율을 높이기 위한 알루미나 등의 재료 첨가가 용이하기 때문이라고 합니다. (다만 첨가물 비중이 증가할수록 접착력이 떨어진다는 단점이 있습니다.)

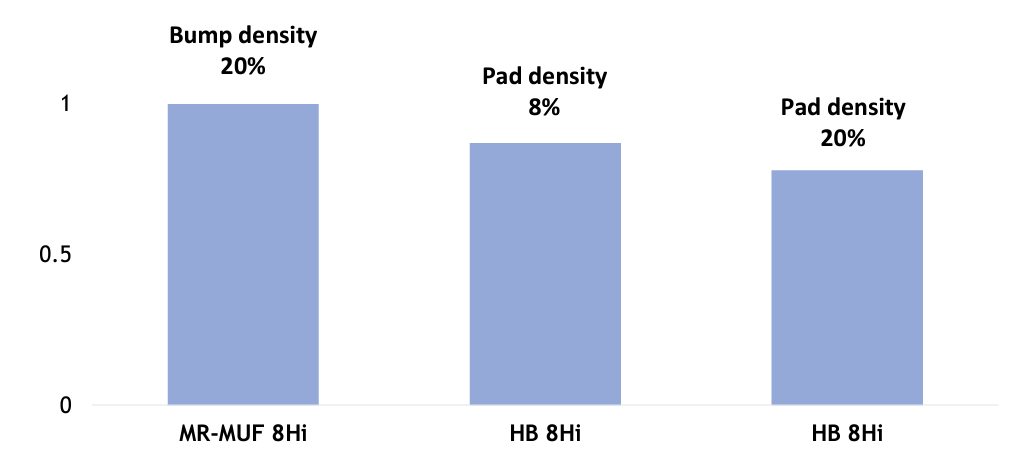

■ 하이브리드 본딩

궁극적으로는 하이브리드 본딩을 통해 기존 HBM Die 사이에 있던 Bump를 제거해 Die간 Gap을 없애고, 이를 통해 열 방출을 방해하는 폴리머 소재의 언더필 공정을 없애는 방향으로 가고 있습니다.

3. 웨이퍼 와피지

DRAM과 VNAND 모두 더 얇게, 더 높게, 더 좁게를 외치면서 발열 뿐만아니라 웨이퍼가 휘는 현상인 와피지(Warpage, Bow) 제어 또한 최근 반도체의 핵심 이슈입니다.

웨이퍼가 휘는 원인은 크게 ▲높은 공정 온도, ▲얇아지는 웨이퍼 두께, ▲무거워지는 반도체가 있습니다.

웨이퍼 와피지는 HBM보다 Flash 메모리인 VNAND에서 먼저 이슈가 되어왔던 문제입니다.

VNAND는 정보가 저장되는 캐패시터 Cell을 수직으로 더 높게 적층하면서 메모리의 용량을 늘려왔습니다.

현재 그 높이가 230단이 넘어가고 있으며, 향후 1000단 이상으로 늘어날 전망입니다.

이렇게 수직으로 높이가 점차 증가하면서 Cell의 가로폭 대비 높이를 뜻하는 종횡비 (A/R, aspcet ratio)가 매우 커지게 됩니다.

종횡비가 커지면서 단위면적당 무게는 점차 증가하고, 높게 쌓인 캐패시터가 무게중심을 잡지 못해 조금만 기울어져도 웨이퍼에 가해지는 압력이 골고루 퍼지지 못해 웨이퍼가 휘게 됩니다.

또한 높이가 높아지면서 이를 Cell 밑에까지 깊게 Etching 하기 위해서는 고온, 고압이 필요한데, 이로 인해 각 소재간 열팽창 계수 차이에 따라 웨이퍼가 휘는 현상이 발생하기도 합니다.

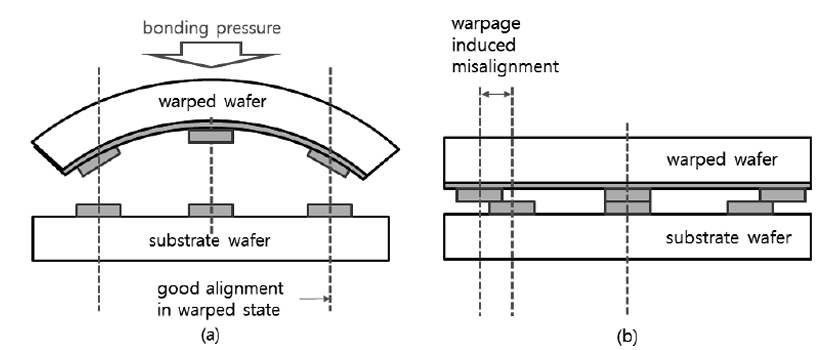

DRAM을 여러층 적층하는 HBM 또한 고온, 고압의 장비를 통해 본딩 공정이 진행되고, TSV라는 구멍을 뚫기 위해 웨이퍼를 얇게 갈아내면서 웨이퍼가 휘게 되는 현상이 발생합니다.

웨이퍼가 휘게 되면 ▲웨이퍼 깨짐, ▲Cell Mis-Align, ▲본딩 Mis-Align 등이 발생해 수율이 크게 떨어집니다.

특히 웨이퍼 레벨 본딩, 웨이퍼 레벨 패키징이 중요한 트렌드로 발전함에 따라 본딩 시 웨이퍼 간 정렬을 맞추는 게 큰 이슈가 되고 있습니다.

이러한 웨이퍼 휨 현상 방지를 위해 웨이퍼 뒷면에 스트레스 완화용 박막을 증착해 웨이퍼를 보강해주거나, 캐리어 웨이퍼 사용, 고온/고압 에칭 공정 대신 극저온 에칭 공정을 쓰는 등의 기술들이 적용되고 있습니다.

댓글