<관련 포스팅>

HBM 제조 공정 기술 분석 : ① TSV(실리콘관통전극) 본딩과 마이크로범프 (차세대 인터커넥션 기술)

HBM 제조 공정 기술 분석 : ② MR-MUF와 TC-NCF 본딩 공정 특징, 차이점, 관련주

HBM 메모리 개요 및 필요성, 기존 DRAM 메모리와의 차이점

1. 어드밴스드 패키징과 본딩 기술

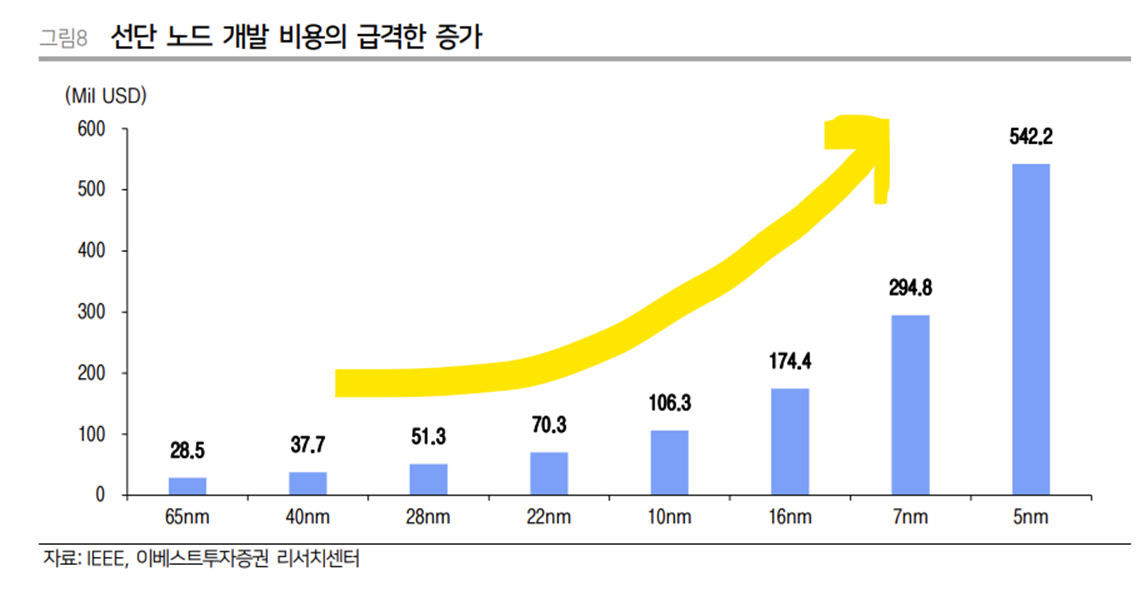

기존 반도체 기술 트렌드는 무어의 법칙에 따라 칩 내 회로의 선폭을 계속 줄여나가는 미세화의 싸움이었습니다.

선폭이 미세화되면 동일 웨이퍼 면적당 생산 가능한 칩 개수가 크게 증가해 규모의 경제를 이룰 수 있고, 트렌지스터의 채널간 길이가 줄어들면서 정보 전달 속도가 증가하고, 저전력 구동이 가능해지기 때문입니다.

그러나 반도체 선폭이 10 나노미터 대의 시대에 접어들면서 물리적인 한계에 도달했고, 공정난이도 상승과 초고가의 반도체 장비 등이 필요해지면서 너무 많은 비용이 투입되고, 수율 또한 잡기 어려워지고 있습니다.

이에 선단 공정 개발에 대한 비용 효율화가 급격히 감소되면서 현대의 반도체 기술 트렌드는 칩 적층 기술과 패키징, 서로 다른 칩을 연결하는 칩렛 기술에 주목하고 있습니다.

모더 댄 무어

(More than Moore)

어드밴스드 패키징 기술의 부각

이러한 적층, 패키징, 칩렛 기술들의 핵심 중 하나는 칩 간, 패키징 간의 연결 기술인 인터커넥션 기술 (본딩 기술) 입니다.

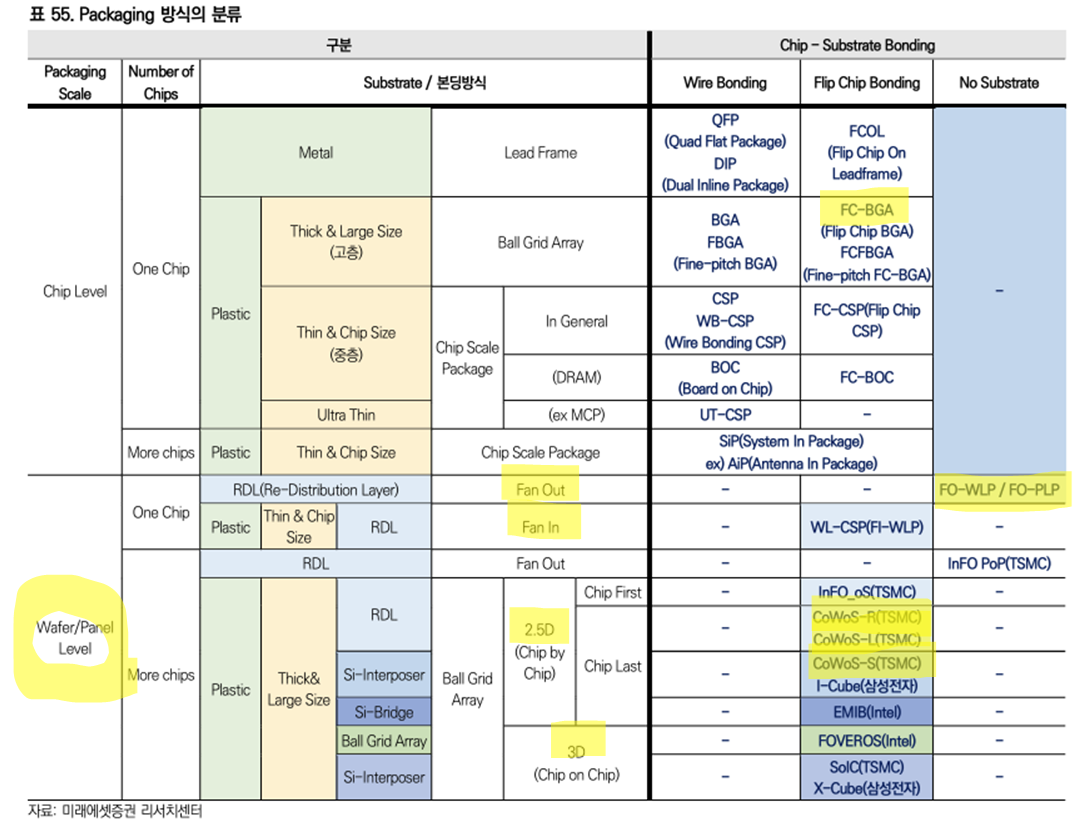

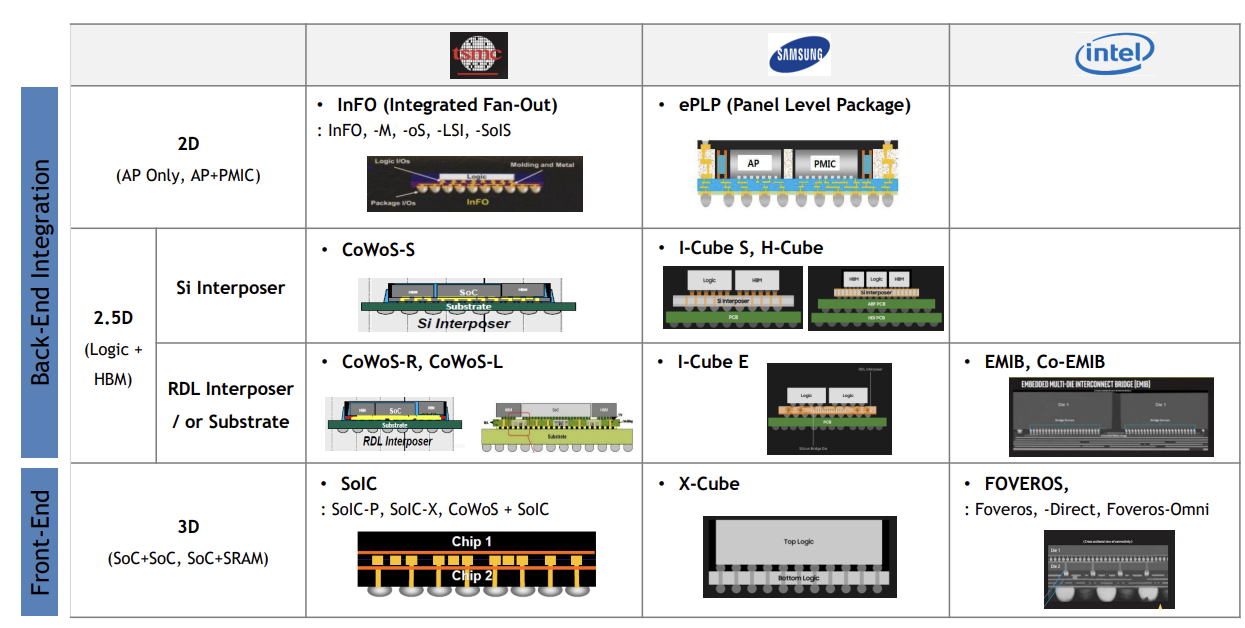

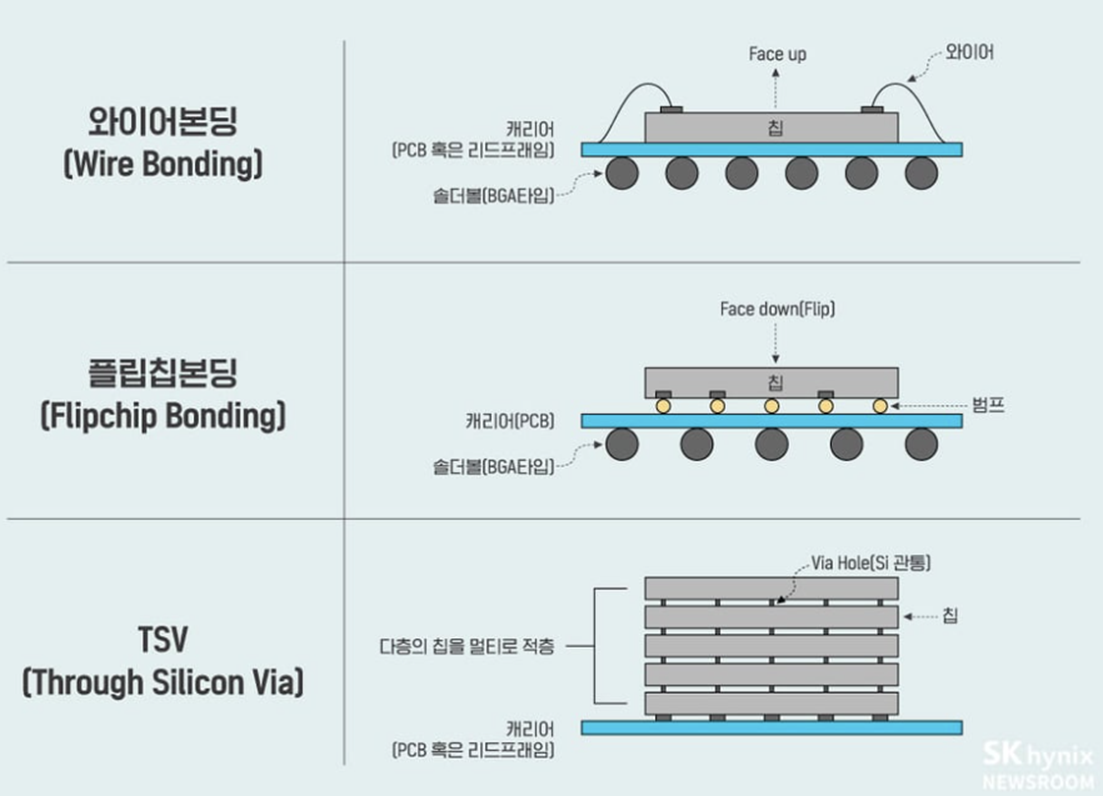

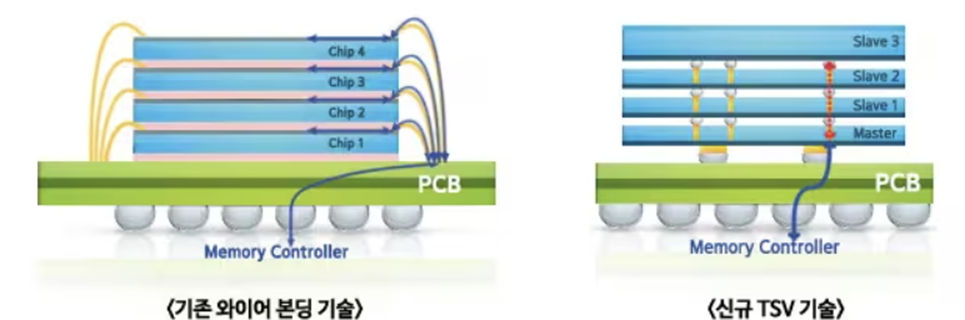

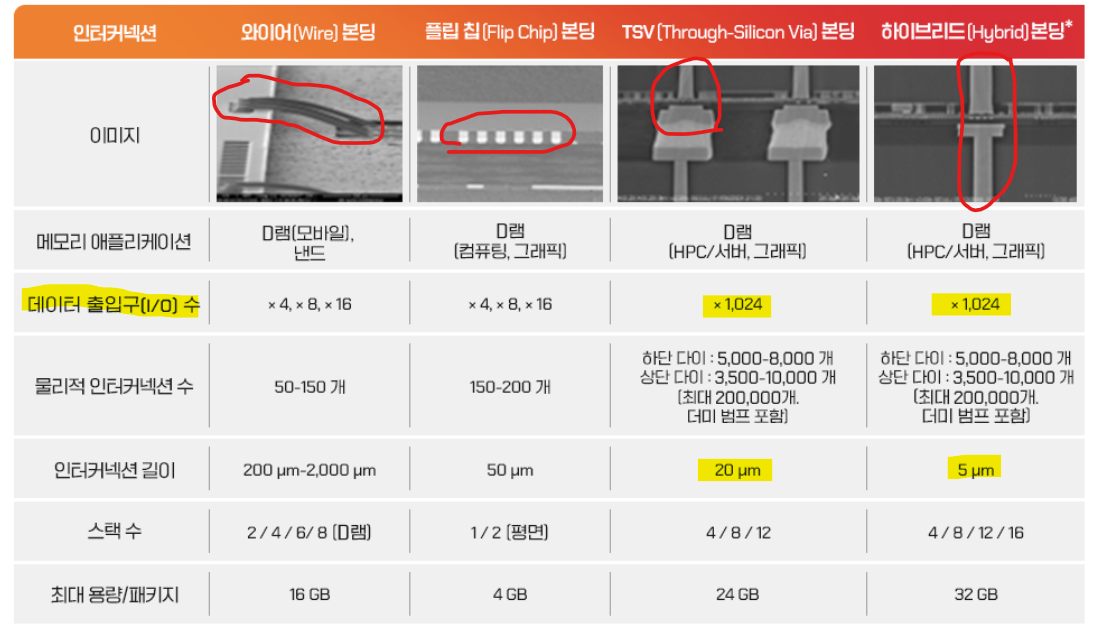

기존에는 주로 구리선 등의 와이어로 칩과 기판을 연결하는 와이어(Wire) 본딩이 사용됐으나, 물리적으로 선의 길이가 길고, 직경이 작아 전기 신호 전달 속도가 느리기 때문에 고속 동작에 한계가 있고, 집적도를 올리기 어려웠습니다.

또한 주로 칩 가장자리에만 와이어 연결이 가능하기 때문에 입출력 개수를 크게 늘리기 어려운 점이 있었습니다.

플립칩(Filp Chp) 본딩은 웨이퍼 전면에 납땜과 같은 다수의 솔더 범프를 만들고, 칩을 뒤집어서 (Flip) 기판과 연결하는 방식입니다. 이는 기존 와이어 방식보다 칩간 길이를 수십분의 1로 줄일 수 있었고, 전기 신호의 통로인 솔더볼을 칩 전면에 만들 수 있기 때문에 입출력(I/O) 개수가 크게 늘어나게 됩니다.

하지만 플립칩 본딩 또한 칩 적층이 불가하고 솔더 범프 자체의 크기와 범프 간 간격 한계 때문에 더 많은 입출력 통로 형성이 불가합니다.

이러한 한계를 해결하기 위해 적층된 칩을 관통해서 서로를 연결하는 TSV 본딩(TC 본딩)이 나타나게 됩니다.

TSV(Through Silicon Via)란 말 그대로 반도체 재료인 실리콘(Silicon)을 뚫어서(Through) 터널을 만들고 그 공간을 구리(Cu)처럼 전기가 통할 수 있는 전도성 재료로 채운 공간(Via)을 말합니다.

즉 반도체 셀(CMOS)이 완성된 웨이퍼를 수직으로 뚫고, 해당 통로 상하단에 칩끼리 접합할 수 있도록 마이크로 범프를 형성한 후 이렇게 만들어진 웨이퍼 여러장을 적층해 붙이는 방식입니다.

이전에는 칩간의 통신을 기판(Subtrate)을 통해 연결했으나 TSV 기술을 통해 칩끼리 바로 통신이 가능해지게 됩니다.

TSV는 기존 본딩 대비 미세한 구멍을 뚫을 수 있기 때문에 칩 한 개 면적에 현재 1024개의 입출력(I/O) 통로를 만들 수 있어 대역폭이 매우 넓고, 칩간 연결 거리가 수직으로 매우 짧아져 전력 소비와 데이터 전송 속도가 크게 향상됩니다.

또한 칩을 적층할 수 있게 되면서 단위 면적당 용량도 크게 늘어나게 됩니다.

따라서 TSV 기술은 DRAM 메모리를 여러개 적층하는 HBM 메모리의 핵심 기술 중 하나가 되었습니다.

그리고 향후 다양한 기능의 여러 칩들을 3D 형태로 적층하고 서로 연결하는 칩렛(Chiplet) 기술로 발전하면서 하이브리드 본딩(Hybrid-Bonding) 기술이 핵심이 되고 있습니다.

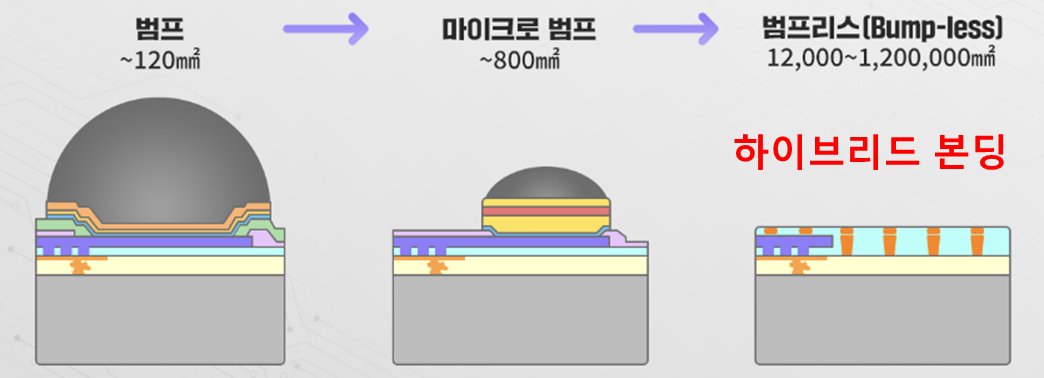

칩렛 기술은 웨이퍼 단계에서 칩과 칩을 연결하는 것이 아니라 패키징까지 완성된 서로 다른 칩들을 3D 적층하여 연결하는 것으로, 칩간 구리 배선끼리 연결하기 위해선 솔더 범프 형성이 필수입니다.

그러나 기존 솔더 범프는 그 크기가 커서 단위 면적당 입출력(I/O) 밀도를 높이는데 한계가 있습니다.

이를 위해 현재의 HBM에서는 마이크로 범프라는 기술을 통해 범프 크기를 줄여 I/O 개수를 늘렸습니다.

그러나 마이크로 범프도 그 크기가 계속 줄어들면서 공정 난이도 상승, 범프간 정렬 틀어짐, 피치간 간격 미세화에 따른 범프 단락 등의 문제가 발생하고 있습니다.

하이브리드 본딩은 솔더 범프를 형성할 필요가 없이 각 칩의 구리 회로간 직접 본딩하거나, 칩 면을 직접 본딩할 수 있는 범프리스(Bumpless) 본딩 기술입니다.

하이브리드 본딩 기술이 도입된다면 칩 적층 높이와 칩간 거리가 감소하면서 패키징 크기가 줄어들고, 단위 면적당 신호의 입출력 개수가 크게 늘어 대역폭을 늘릴 수 있습니다.

또한 회로 길이가 짧아지면서 고속 동작이 가능하고, 저항이 감소하면서 방열 특성 또한 개선됩니다.

이렇듯 차세대 반도체 기술은 웨이퍼 단계(전공정)를 넘어 패키징 단계(후공정)에서 어떻게 칩간 거리와 패키징 크기를 줄이고 신호 입출력 개수를 늘려 단위 면적당 대역폭과 속도를 증가시킬 수 있을지에 집중하고 있습니다.

따라서 이에 핵심인 인터커넥션 본딩 기술을 눈여겨 봐야합니다.

2. 관련주

작성중...

'산업 및 기업 분석 > 반도체·디스플레이' 카테고리의 다른 글

| [HBM 파헤치기기] HBM 제조 공정 기술 분석 : ③ 핵심은 발열과 웨이퍼 와피지 컨트롤 (1) | 2024.06.07 |

|---|---|

| [HBM 파헤치기] HBM 제조 공정 기술 분석 : ② MR-MUF와 TC-NCF 본딩 공정 특징, 차이점, 관련주 (4) | 2024.05.19 |

| [HBM 파헤치기] HBM 제조 공정 기술 분석 : ① TSV(실리콘관통전극) 본딩과 마이크로범프 (차세대 인터커넥션 기술) (0) | 2024.05.12 |

| [HBM 파헤치기] HBM 메모리 개요 및 필요성, 기존 DRAM 메모리와의 차이점 - AI 반도체의 핵심! (2) | 2024.03.10 |

댓글